All-in-One Android Touch Screen/zh

From FriendlyELEC WiKi

1 介绍

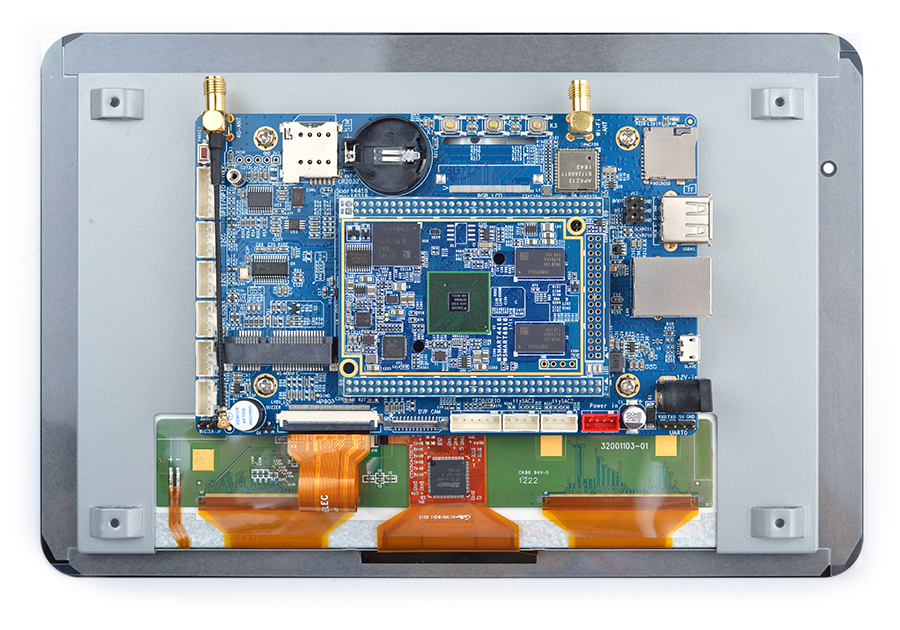

- All-in-One Android Touch Screen是友善电子最新设计开发并生产的一款9寸高清安卓触摸显示解决方案,搭载使用八核Cortex-A53的三星S5P6818作为主处理器的高性能Smart6818核心板,处理器运行主频可高达1.4Ghz,并标配1GB DDR3内存和8GB eMMC高速闪存,不仅集成电源管理单元,实现了软件开关机和硬件唤醒功能,还集成了Wi-Fi、蓝牙、千兆以太网卡和声卡芯片,支持EC20 4G模块,非常方便企业用户进行快速产品设计和项目开发。 支持1280 x 800分辨率显示,支持触摸,背光通过i2c通讯调节。提供I2C、SPI、UART、USB等常用接口,非常方便企业用户做二次开始使用。

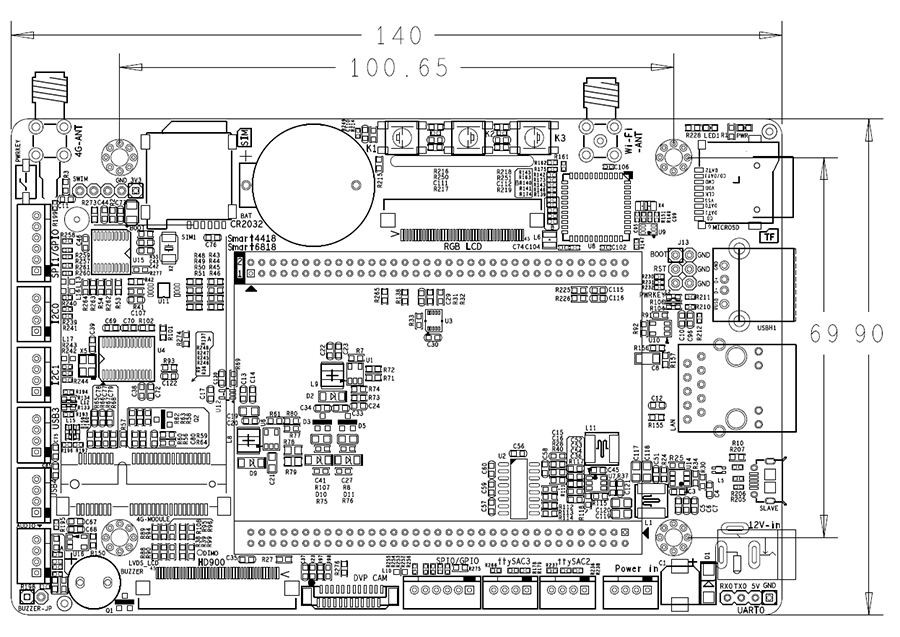

2 机械尺寸图

3 接口定义

- HD900(LVDS)接口定义

Pin# Symbol I/O Function 1 VDD-C-TP P Power supply input for C-TP 2 GND-C-TP P Ground for C-TP 3 RST-C-TP I Reset C-TP 4 SCL I I2C Clock 5 SDA I/O I2C Data 6 INT O Interrupt pin 7 GND P Ground 8 GND P Ground 9 GND P Ground 10 VCOM P Common Voltage 11 VDD P Power Voltage for digital circuit 12 VDD P Power Voltage for digital circuit 13 RST GLOBAL I Global reset pin 14 STBYB I Standby mode 15 GND P Ground 16 RXIN0- I -LVDS differential data input 17 RXIN0+ I +LVDS differential data input 18 GND P Ground 19 RXIN1- I -LVDS differential data input 20 RXIN1+ I +LVDS differential data input 21 GND P Ground 22 RXIN2- I -LVDS differential data input 23 RXIN2+ I +LVDS differential data input 24 GND P Ground 25 RXCLKIN- I -LVDS differential clock input 26 RXCLKIN+ I +LVDS differential clock input 27 GND P Ground 28 RXIN3- I -LVDS differential data input 29 RXIN3+ I +LVDS differential data input 30 GND P Ground 31 GND P Ground 32 DIMO O Backlight CABC controller signal output 33 SELB I 6/8bit mode select 34 AVDD P Power for Analog Circuit 35 GND P Ground 36 LED- P LED Cathode 37 LED- P LED Cathode 38 L/R I Horiaontal inversion 39 U/D I Vertiacl inversion 40 VGL P Gate OFF Voltage 41 CABCEN1 I CABC H/W enable 42 CANCEN0 I CABC H/W enable 43 VGH P Gate ON Voltage 44 LED+ P LED Anode 45 LED+ P LED Anode

- DVP CAM 接口定义

Pin# Name Function 1, 2 SYS_3.3V 3.3V power output, to camera modules 7,9,13,15,24 GND Gound, 0V 3 I2C2_SCL I2C Clock Signal 4 I2C2_SDA I2C Data Signal 5 GPIOE15 Regular GPIO, control signals output to camera modules 6 GPIOE14 Regular GPIO, control signals output to camera modules 8 MCLK Clock signals output to camera modules 10 NC Not Connected 11 VSYNC vertical synchronization to CPU from camera modules 12 HREF/HSYNC HREF/HSYNC signal to CPU from camera modules 14 PCLK PCLK signal to CPU from camera modules 16-23 Data bit7-0 data signals

4 支持的开发板

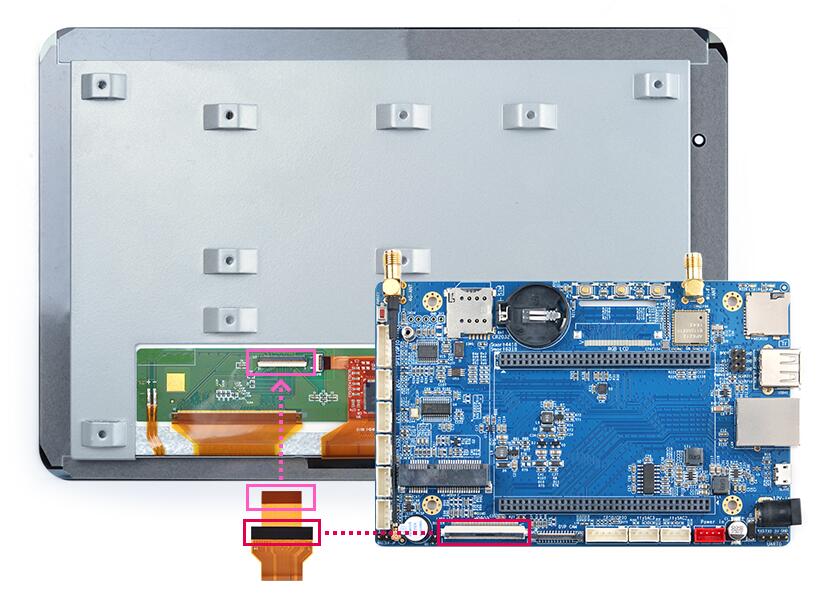

5 连接使用

6 原理图下载

- [点击下载]